# THE PCD February 2015 CLESSEDNE MAGAZINE

an ICOnnect007 publication

Effects of Surface Roughness on High-speed PCBs — p.22

I<sup>3</sup>: Incident, Instantaneous, Impedance — p.28

Effects of DC Bias on Ceramic Capacitors — p.34

Controlled Impedance: A Real-World Look at the PCB Side — p.38

The base for imovation

Insertion Loss: A Bigger Concern in High-Speed Digital? — p.44

# **HIGH-SPEED DESIGN**

# **PCB BUYERS**compare nearly 1900 manufacturers now at The PCB List.

**Quick Search**

Advanced Search

The best way to find a PCB fabricator, anywhere.

### www.thepcblist.com

# **DESIGN NEWS**

| DFX — Design for Excellence                                                                            |                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Technical education with a design focus                                                                |                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| February 20–26, 2015                                                                                   | <ul> <li>IPC APEX EXPO in San Diego, CA</li> <li>Premier industry event features a range of design offerings</li> <li>Professional development courses — three hours of classroom instruction led by SMEs</li> <li>Design Forum — a day of technical presentations from thought leaders in design</li> <li>Designer Certification</li> </ul> |  |  |  |

| IPC Designer Certification                                                                             |                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| CID (Certified Interconnect Designer-Basic) and CID+ (Advanced) are valuable professional credentials, |                                                                                                                                                                                                                                                                                                                                              |  |  |  |

CID (Certified Interconnect Designer-Basic) and CID+ (Advanced) are valuable professional credentials, earned in three-day sessions that include classroom instruction and testing.

#### **USA** sessions

| February 20–22, 2015 CID and CID+ | San Diego, CA<br>in conjunction with IPC APEX EXPO |

|-----------------------------------|----------------------------------------------------|

|-----------------------------------|----------------------------------------------------|

For USA sessions register at +1-800-643-7822.

New edition of CID and CID+ course materials will be available starting January 2015.

#### If you are not already Certified:

Be sure to include the program in your budget for next year — contact your training center for information about class schedule and fees.

IPC Designers Council Members Only SUBSCRIBE An international society for individuals with interest in design. No fees, only benefits — like discounts on designated IPC documents.

Already in Designers Council? Be sure you can access the IPC technical forum for designers worldwide — subscribe at left.

#### **FEATURED CONTENT**

A decade ago, most PCB designers didn't have to worry about the challenges associated with higher speeds. But now, many electronic products feature high-speed PCBs, and designs are getting faster all the time. This month, we focus on high-speed design techniques, with articles from our contributors Kirk Fabbri, Barry Olney, Istvan Novak, Martyn Gaudion, John Coonrod, and Bob Tarzwell and Dan Beaulieu.

#### 10 Effective Characteristic Impedance

by Kirk Fabbri

#### FEATURE COLUMNS

- 22 Effects of Surface Roughness on High-speed PCBs by Barry Olney

- 28 I<sup>3</sup>: Incident, Instantaneous, Impedance

by Martyn Gaudion

#### FEATURE COLUMNS

34 Effects of DC Bias on Ceramic Capacitors by Istvan Novak

**38 Controlled Impedance: A Real-World Look at the PCB Side** by Dan Beaulieu and Bob Tarzwell

44 Insertion Loss: A Bigger Concern in High-Speed Digital? by John Coonrod

# **Sola** *RF/Microwave Materials & Resources*

- IS680 materials offers a complete laminate materials solution for single- and double-sided printed circuit designs and is a cost-effective alternative to PTFE and other commercial microwave materials.

- I-Tera® MT RF materials are available in 0.010", 0.020" and 0.030" in 3.38, 3.45 and 3.56 Dk.

- I-Tera® MT materials are suitable for both high-speed digital and RF/ microwave designs. A full compliment of cores and prepregs allowing flexibility in design is available in core thicknesses from 0.002" to 0.018".

- TerraGreen® halogen-free, very low-loss, thermoset materials are available in a variety of laminate and prepreg offerings. This material is inexpensive to process – improving your company's bottom line, as well as the environment.

- The revolutionary Astra® MT ultra low-loss thermoset laminates are a replacement for PTFE. These materials have been used for hybrid applications with Isola's 185HR and 370HR products.

|                                                         | RF/MICROWAVE MATERIALS                   |                            |                        |                 |                 |

|---------------------------------------------------------|------------------------------------------|----------------------------|------------------------|-----------------|-----------------|

|                                                         | <b>IS680</b>                             | I-Tera® MT RF              | I-Tera <sup>®</sup> MT | TerraGreen®     | Astra® MT       |

| Tg                                                      | 200°C                                    | 200°C                      | 200°C                  | 200°C           | 200°C           |

| Td                                                      | 360°C                                    | 360°C                      | 360°C                  | 390°C           | 360°C           |

| Dk @ 10 GHz                                             | 2.80 - 3.45                              | 3.38, 3.45 & 3.56          | 3.45*                  | 3.45*           | 3.00            |

| Df @ 10 GHz                                             | 0.0028 - 0.0036                          | 0.0028, 0.0031 &<br>0.0034 | 0.0031*                | 0.0030*         | 0.0017          |

| CTE Z-axis (50 to 260°C)                                | 2.90%                                    | 2.80%                      | 2.80%                  | 2.90%           | 2.90%           |

| T-260 & T-288                                           | >60                                      | >60                        | >60                    | >60             | >60             |

| Halogen free                                            | No                                       | No                         | No                     | Yes             | No              |

| VLP-2 (2 micron Rz copper)                              | Available                                | Available                  | Available              | Standard        | Standard        |

| Stable Dk & Df over the temperature range               | -55°C to +125°C                          | -55°C to +125°C            | -55°C to +125°C        | -55°C to +125°C | -40°C to +140°C |

| Optimized global constructions for Pb-free assembly     | Yes                                      | Yes                        | Yes                    | Yes             | Yes             |

| Compatible with other Isola products for hybrid designs | For use in double-<br>sided applications | Yes                        | Yes                    | Yes             | Yes             |

| Low PIM < -155 dBc                                      | Yes                                      | Yes                        | Yes                    | Yes             | Yes             |

\* Dk & Df are dependent on resin content NOTE: Dk/Df is at one resin %. Please refer to the lsola website for a complete list of Dk/Df values. The data, while believed to be accurate & based on analytical methods considered to be reliable, is for information purpos only. Any sales of these products will be governed by the terms & conditions of the agreement under which they are sold.

#### **RF Conversion Service**

- Isola's Design Review Service can facilitate your conversion to Isola's RF/microwave products and get you to market faster with the newest, ultra-low-loss materials.

- As part of this new service, Isola's technical staff will provide turn-key calculations, testing, characterizations and material recommendations to assist PCB fabricators and OEMs in converting to Isola's RF-materials, which will help overcome the current material shortages of other vendors and accelerate time-to-market. The design review service will also address the perceived conversion issues when migrating from a currently used material to an Isola material.

#### http://www.isola-group.com/conversion-service

#### **FREE! Impedance and Power-Handling Calculator**

- Isola's free Impedance and Power-Handling Calculator predicts the design attributes for microstrips and striplines based on the design's target impedance and dielectric properties of the company's RF, microwave and millimeter-wave laminate materials.

- This software tool provides a design or an equivalent dielectric constant to facilitate modeling for PCB designers to predict impedance and other design attributes. The software computes changes in the effective dielectric constant due to dispersion at higher frequencies. The software then computes the total insertion loss a measure of power lost through heat for power handling calculations, including the dielectric loss, conductor loss, and the loss due to the surface roughness. The main factors affecting the typical power-handling capability of a material are its thermal conductivity, the maximum operating temperature, and the total insertion loss.

#### https://isodesign.isola-group.com/phi-calculator

## www.isola-group.com/RF

Isola, I-Tera, TerraGreen, Astra and IsoDesign and the Isola logo are registered trademarks of ISOLA USA Corp. in the U.S.A. and other countries. All othe trademarks mentioned herein are property of their respective companies. Copyright © 2015 Isola Group. All rights reserved. FEBRUARY 2015

**VOLUME 4**

NUMBER 2

thepcbdesignmagazine.com

an ICONNECt007 publication

THE OPTIMUM

MAGAZINE

DEDICATED TO

PCB DESIGN

#### CONTENTS

SHOW PREVIEW54 2015 IPC APEX EXPO Show Preview

#### COLUMNS

8 IPC Updates CID, and DFX Takes Off by Andy Shaughnessy

**50** Push the Button, Max by Tim Haag

VIDEO INTERVIEW 27 HKPCA Keynote Speech: EMS Trends for 2015

#### NEWS HIGHLIGHTS

- 42 PCB007

- 48 Mil/Aero007

- 62 PCBDesign007

#### EXTRAS

- 64 Events Calendar

- 65 Advertiser Index & Masthead

# Pulsonix

Advanced Schematic Capture and PCB Design Software

# A refreshing approach to simplifying Schematic Capture and PCB Design

- Import filters for all major tools (designs and libraries)

- Very easy to learn and use

- 5-Star Service and Support

Download a Free Trial

info@pulsonix.com www.pulsonix.com

#### THE SHAUGHNESSY REPORT

## **IPC Updates CID**, and DFX Takes Off

#### by Andy Shaughnessy

I-CONNECT007

It's almost time for IPC APEX EXPO 2015, and I, for one, am happy to be returning to the San Diego Convention Center. Is there a nicer city in America than San Diego? Yes, it's a tad expensive, but it's worth it; there are worse places to spend a week. Nothing against Las Vegas, but San Diego beats Sin City in every category, with the exception of hotel rooms per square mile.

The Design Forum kicks off the show on the morning of Feb. 23, with a variety of new classes and speakers. This marks the first Design Forum since the death of Dieter Bergman. It'll be bittersweet, but I'm sure everyone will be sharing stories about Dieter. (Everyone is invited to join the tribute to Dieter on Wednesday, Feb. 25, at 6:30 pm in Ballroom 6F in the convention center. Share your memories of Dieter, or some of his best off-color jokes, or your favorite "Dieterisms." The \$25 admission goes to a scholarship fund in Dieter's name.)

After a networking breakfast, PCB design engineer Carl Schattke of Tesla Motors will give the keynote speech. Have you ever met anyone who designed boards for electric cars? That should draw a pretty good crowd. Then IPC Master Trainer Rainer Taube of Taube Electronic GmbH will discuss IPC-7070 component mounting issues. Tom Hausherr of PCB Libraries will wrap up the morning, focusing on IPC-7351C, requirements for surface mount design and land pattern standard.

After lunch, the Professional Development design classes begin. Stephen V. Chavez, a PCB designer with UTC Aerospace Systems who has spent a lot of time working abroad, will offer tips for communicating and working with multicultural design teams. From what I've heard,

#### **IPC UPDATES CID, AND DFX TAKES OFF** continues

this will be a really interesting talk. The day wraps up with the newly retired (but will he ever really retire?) Rick Hartley discussing ways to achieve success by controlling cost and quality. And isn't cost and quality what it's all about?

#### **IPC Design Programs Update**

You may have heard that the IPC Certified Interconnect Designer program (CID and the CID+ advanced course) has been updated. Course content has been fine-tuned periodically since the program was introduced 20 years ago, but the 2015 edition is a completely refreshed program. CID and CID+ tutorials and exam take place Feb. 20-22 at the convention center.

I spoke with Anne Marie Mulvihill, director of education programs at IPC, and asked her about the technical offerings for PCB designers.

"If I look tired at the show, it's because I've proofed the new edition about 87 times," she laughed. "This material isn't easier; it's just easier to digest, and or-

ganized to synch up CID to CID+ for better flow of information. Designers who are already certified won't require recertification to this 2015 edition, but they should consider reviewing the new study guides, just to stay current with best practices."

She pointed out how designers can use the CID study guide to show their bosses and teammates what they've been studying, and what their job entails.

"Nobody puts baby in the corner, but designers still wind up there. Designers are not getting the respect they deserve, and new hires need formal training," Anne Marie said. "So, let your boss see this study guide. Make a 10-minute appointment to show your boss just a sample of what you're doing, or schedule time at your next department meeting for a brief presentation to your whole team. Communication can really pay off."

"Nobody puts baby in the corner, but designers still wind up there. Designers are not getting the respect they deserve, and new hires need formal training," Anne Marie said. "So, let your boss see this study guide.

For certified designers who want to take their professional development to the next level, she recommends DFX - Design For Excellence: DFM, DFA, DFT, and more. This full-day DFX course takes place Sunday, Feb. 22 at IPC APEX EXPO in San Diego.

"The DFX course debuted in late 2013, and it's been a door-buster ever since. It provides all teams a better understanding of all phases of the product lifecycle. Not just design, but manufacturing, all the way through to test phase," she added. "And if you can't get to San Diego, we're bringing the DFX course to a theater near you! We're holding DFX courses in Texas in May, Chicago in June, Minneapolis in October, and Raleigh in December."

> The DFX class can be provided on-demand for interested companies or Designers Council chapters.

The second component of the IPC DFX program is an industry guideline in development now, and scheduled for pub-

lication this fall. Anne Marie expressed special thanks to the core members of the DFX Document Committee for their work developing this course: Don Dupriest of Lockheed Martin, Karen McConnell of Northrup Grumman, Dale Lee of Plexus, and Cheryl Tulkoff of DfR Solutions. Cheryl and Dale are the instructors for the DFX course.

For more information on IPC courses in 2015, <u>click here</u>. For a list of IPC-licensed training centers <u>click here</u>.

See you at APEX and the Design Forum. **PCBDESIGN**

Andy Shaughnessy is managing editor of *The PCB Design Magazine.* He has been covering PCB design for 15 years. He can be reached by clicking here.

reature

by Kirk Fabbri KSPT ENGINEERING CONSULTING

In a typical interconnect, there lie multiple places where capacitance plays a factor in the signal integrity. This includes the driver and receiver output/input capacitance, as well as the packages, vias, and the transmission lines. Failing to optimize these parameters can often lead to unwanted reflections, excessive radiated and or conducted emissions, and sometimes failure of components and systems.<sup>1</sup>

Reflections can occur anytime there is an impedance mismatch on the line. Sources of mismatches are plentiful and include trace width changes, vias, stubs, reference plane changes, and even the so-called fiber weave effect. In this case, a trace can encounter a different dielectric constant depending on whether it is routed over glass or the epoxy resin in the dielectric material.<sup>3</sup>

In this investigation, it is the capacitive contribution of the different components that are of interest, and how they affect the characteristic impedance the driver sees. For the following examples, the HyperLynx Termination Wizard is used for investigating these effects. It works on a variety of termination schemes including series, parallel, Thevinin, AC, and combinations of those topologies.

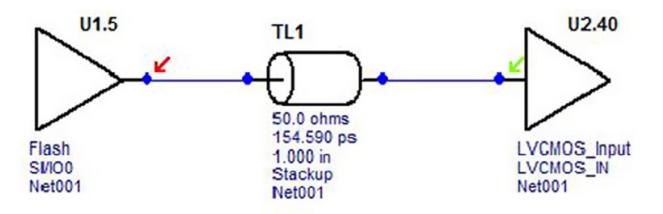

Figure 1 shows a simple point-to-point system in HyperLynx 9.0 LineSim. Included is a driver (flash signal I/O pin) and a simple LVC-MOS input connected by a one-inch, 50-ohm transmission line.

Running the termination wizard on this net reveals the following results shown in Figure 2. The wizard shows that the driver impedance is 52.7 ohms (based on the IBIS model pull-up/ pull-down curves and the 50-ohm load line), the driver transition time is 855ps, the characteristic impedance of the transmission line is 50 ohms, and the effective impedance is 46.5

# NISSION:

Our partnership with eSurface is making the impossible totally possible ...without increased cost. Designers have more freedom and creativity without compromising manufacturing viability.

#### Key advantages include:

- Higher yield on finer features

- Finest lines and spaces available

- With a unique covalent bond, it is possible to metallize to virtually any substrate

Murrietta Circuits is proud to be the ONLY eSurface Licensed Manufacturer in Southern California!

Click to learn more,

www.murrietta.com | (714) 970-2430

Figure 1: The schematic diagram for a simple circuit consisting of a driver (U1.5) and receiver (U2.40) connected by a one-inch, 50-ohm transmission line.

| Terminator analysis                                     |   | Termination suggestions                                       |

|---------------------------------------------------------|---|---------------------------------------------------------------|

| Net name: Net001                                        |   | Apply Values                                                  |

| Number driver IC's: 1                                   |   |                                                               |

| Number receiver IC's: 1                                 |   |                                                               |

| Number resistors: 0                                     |   |                                                               |

| Number capacitors: 0                                    |   |                                                               |

| Driver impedance: 52.7 ohms                             |   |                                                               |

| Driver transition time: 0.855 ns                        | = |                                                               |

| Total net length, not                                   |   |                                                               |

| including packaging: 1.000 in                           |   | Apply tolerance:                                              |

| Impedance Z0: 50.0 ohms                                 |   | Exact Value 🗸 🗸                                               |

| Effective Z0: 46.5 ohms                                 |   |                                                               |

|                                                         |   | Hints                                                         |

| Termination found: none                                 |   | Effective impedance includes                                  |

| Driver to receiver: should be < 0.922 in                |   | the average line impedance                                    |

| Termination suggested: series resistor                  |   | and receiver loading.                                         |

|                                                         | - | Delays are copper only; IC                                    |

| Messages:                                               |   | loading/thresholds and signa<br>reflections are not included. |

| Net is source-terminated by driver impedance.           |   |                                                               |

| Wide driver impedance tolerance may hinder termination. | - | Preferences.                                                  |

|                                                         |   |                                                               |

|                                                         |   | OK                                                            |

|                                                         |   | Help                                                          |

Figure 2: Termination wizard results for the simple schematic shown in Figure 1.

ohms. The effective impedance (effective Z0) is explained in the LineSim user guide as a value calculated by the field solver to indicate how much the capacitance of the load IC decreases the impedance the driver sees.<sup>2</sup> As shown later, the effective Z0 calculation is highly dependent on several key parameters.

To understand the effective Z0 parameter, the IBIS model of the receiver is investigated. For those who aren't familiar with the IBIS format; IBIS is used to show the buffer's behavior without compromising the manufactures proprietary information. An IBIS model describes the transistor pull-up/pull-down curves, the ESD diode clamp curves, the drivers' transition characteristics, pin parasitic information, and package model parameters among others. Figure 3 is an excerpt from the receiver's IBIS model showing the package parameters for the IC.<sup>4</sup> Figure 4 shows both the pin RLC parameters and the value C\_comp under the appropriate buffer model.

#### Capacitive Effects on Effective Characteristic Impedance

Most interesting are the package/pin parasitic capacitance and the parameter C\_comp in the receiver model. It is important to note the pin RLC parameters for this model were added for demonstration purposes and do not truly represent the buffer characteristics.

In this case, the addition of the package capacitance (0.605pF), the pin capacitance (2pF), and input capacitance (0.5pF) make up the total input load capacitance. According to the wizard, it is this capacitive load that effectively lowers the characteristic impedance that the driver sees down to 46.5 ohms. In this case the driver impedance (52.7 ohms) is already higher than the characteristic impedance, so no additional termination is recommended.

For demonstration purposes, the pin capacitance is changed to something significantly higher (10pF for this example). Running the wizard for this case indicates that the effective Z0 is now 39.4 ohms, as shown in Figure 5.

Now the pin capacitance is set to 0pF to analyze C\_comp's contribution to the results. After running the wizard on this scenario, the results show the effective Z0 to be 43.9 ohms, indicating that C\_comp also has an impact on the impedance the driver sees.

| [Package] | typ      | min                  | max      |

|-----------|----------|----------------------|----------|

| R_pkg     | 85.000m  | 45.0500m             | 0.1039   |

| L_pkg     | 3.7700nH | 3.4000nH             | 4.1550nH |

| C_pkg     | 0.6050pF | $0.5440 \mathrm{pF}$ | 0.6650pF |

| 1         |          |                      |          |

Figure 3: Receivers RLC package parameters for the IC. IBIS includes the minimum, typical, and maximum values for all parameters.

| 38<br>39<br>40 | VDD_IO<br>PCLK_OP<br>LVCMOS_IN | POWER<br>PRU08slew_ESD<br>PRU08slew | 0.1  | 1.5nH | 2pF |

|----------------|--------------------------------|-------------------------------------|------|-------|-----|

| C_comp         | 0.5000pF                       | 0.5000pF                            | 0.50 | )00pF |     |

Figure 4: Pin RLC parameters for pin 40 (RGBA0) and the values for C\_comp. The pin RLC data was added to the model for demonstration purposes. C\_comp is the input capacitance for the buffer when specified as an input and the output capacitance when specified as an output.

| Terminator analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | Termination suggestions                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Net name:       Net001         Number driver IC's:       1         Number receiver IC's:       1         Number resistors:       0         Number capacitors:       0         Driver impedance:       52.7 ohms         Driver transition time:       0.855 ns         Total net length, not       1.000 in         Impedance Z0:       50.0 ohms         Effective Z0:       39.4 ohms         Termination found:       none         Driver to receiver:       should be < 0.922 in         Termination suggested:       series resistor | 4 III | Apply Values Apply tolerance: Exact Value Hints Effective impedance includes the average line impedance and receiver loading. Delays are copper only; IC loading/thresholds and signal |

| Messages:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | reflections are not included.                                                                                                                                                          |

| Net is source-terminated by driver impedance.<br>Wide driver impedance tolerance may hinder termination.                                                                                                                                                                                                                                                                                                                                                                                                                                  | *     | Preferences.                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | Help                                                                                                                                                                                   |

Figure 5: The wizard results after changing the capacitance parameter of the pin to 10pF. Notice how the effective Z0 is considerably lower than previously shown.

## Transmission Line's Effect on Effective Characteristic Impedance

The length of the transmission line also had an effect on the results of the wizard. Recall from Figure 1-1 that the driver and receiver are connected by a 1 inch 50 ohm transmission line. Figure 6 below shows the transmission line parameters calculated by the field solver where the inductance (L) and capacitance (C) are the results of the entire one-inch of transmission line.

Depending on which source is referenced, publications differ on when the interconnect is considered to be a lumped or distributive system.<sup>1</sup> This distributive property is based on the drivers transition rate as compared to the delay of the interconnect. The field solver appears to using a  $1/6^{\text{th}}$  rule as based on the experiment outlined next.

For this experiment, the length of the transmission line is shortened to see where the wizard starts to ignore its effect on the effective Z0 parameter. The receiver IBIS model is set back to its original configuration with C\_comp being equal to 0.5pF and the pin RLC parameters set to equal those shown in Figure 4. Recall from Figure 2 that the effective Z0 was equal to 46.5 ohms by this configuration.

Now the transmission line is shortened to 0.5 inches to see the effect on the wizard. Figure 7 shows the results after shortening the trans-

# How can you find the best PCB Partner? We can tell you. We wrote the book on it.

Since 1985, U.S. Circuit has been a premier supplier of both commercial and military Printed Circuit Boards in the United States. We know what it takes to be a good PCB partner. And we want to share what we've learned with you.

Choosing a PCB partner isn't hard—if you know what to look for. We've broken it down into "The 5 Commandments" and you can download it for free.

We are proud to be the Circuit Board Manufacturer of more than 400 growing companies, and even prouder to be a good partner for all our customers!

#### Click to Download

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

| Transmission-Line Type V<br>Transmission-line type          | alues Loss                                      | Transmission-line        | e properties    |                  |

|-------------------------------------------------------------|-------------------------------------------------|--------------------------|-----------------|------------------|

| Uncoupled (single line)                                     | Coupled                                         | Name:                    |                 |                  |

| <ul> <li>Simple</li> <li>Stackup</li> </ul>                 | Stackup                                         | Z0:                      | 50.0            | ohms             |

| <ul> <li>Microstrip</li> </ul>                              | Jackup                                          | Delay:                   | 0.155           | ns               |

| Buried Microstrip                                           |                                                 | R:                       | 0.148           | ohms             |

| Stripline Wire Over Ground                                  |                                                 | Comment:                 | Stackup         |                  |

| Cable                                                       |                                                 |                          | = 7.7 nH        |                  |

| Connector                                                   |                                                 |                          | = 3.1 pF        |                  |

|                                                             | Coupling direction                              | Hint<br>R is the DC resi | stance of the t | ansmission line. |

|                                                             | <ul> <li>Dot Right</li> <li>Dot Left</li> </ul> |                          |                 |                  |

| Hints                                                       |                                                 | - Transmission line      | e to paste      |                  |

| If your lines are mostly on t<br>"stackup" is the best type |                                                 |                          |                 | Сору             |

| For information on coupled<br>coupling dots, see Hints.     | lines or Hints                                  |                          |                 | Paste            |

|                                                             |                                                 |                          |                 |                  |

|                                                             |                                                 |                          |                 |                  |

Figure 6: The important parameters for the 50 ohm transmission line.

mission line to 0.5 inches. Notice now that the effective Z0 is equal to the transmission line Z0 parameter of the system—50 ohms. From this it is reasonable to conclude that the simulator no longer considers this to be a distributive system since the length of the interconnect is shorter than some factor when compared to the driver transition time.

#### 1/6<sup>th</sup> Rule

Now the interconnect length is changed to be 1/6<sup>th</sup> of the driver transition time, which according to the wizard is 855ps. This transition time would equate to an interconnect delay of approximately 142.5ps. Using the original transmission line delay factor of 155ps/ inch, the line length is calculated to be approximately 0.919 inches. After running this simulation, the wizard indicates that the field solver still considers the system lumped, and therefore, not considering the interconnect length in the effective Z0 calculations. If the interconnect length is set just slightly longer than this 1/6<sup>th</sup> factor (e.g., 0.925 inches), the simulator switches over to a distributive system and the effective Z0 parameter decreases to 48.1 ohms from 50 ohms (lumped system calculation).

Also notice that 48.1 ohms is calculated for a transmission line length of 0.925 inches, which is slightly larger than for the one-inch line (46.5 ohms). Since the line length is slightly less, the total distributed capacitance is also less, thus the driver's loading is decreased, mak-

| erminator Wizard                                                                                                                                                                                                                                               |                                                                                 |   | 23                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------|

| Terminator analysis<br>Net name:<br>Number driver IC's:<br>Number receiver IC's:<br>Number resistors:<br>Number capacitors:<br>Driver impedance:<br>Driver transition time:<br>Total net length, not<br>including packaging:<br>Impedance Z0:<br>Effective Z0: | 1<br>1<br>0<br>0<br>52.7 ohms<br>0.855 ns<br>0.500 in<br>50.0 ohms<br>50.0 ohms |   | Apply Values Apply Values Apply tolerance: Exact Value Hints Effective impedance includes the average line impedance and receiver loading. |

| Pin-to-pin lengths<br>Messages:                                                                                                                                                                                                                                |                                                                                 |   | Delays are copper only; IC<br>loading/thresholds and signal<br>reflections are not included.                                               |

|                                                                                                                                                                                                                                                                |                                                                                 | * | Preferences<br>OK<br>Help                                                                                                                  |

Figure 7: Results of the wizard after the transmission line length is shortened to 0.5 inches. Notice the effective Z0 is equal to the impedance Z0 parameter of the system—50 ohms.

ing the effective Z0 increase (recall the effective Z0 results from Figure 5).

#### **Simple Series Terminated Circuit**

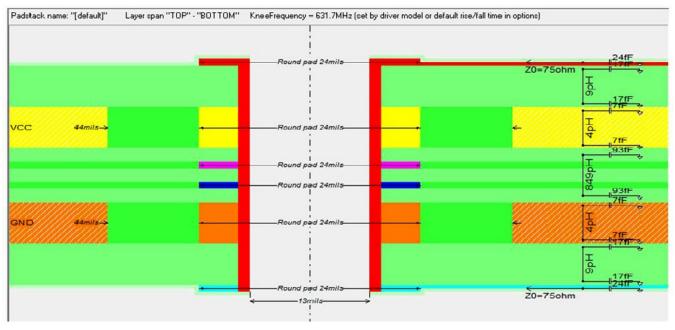

Figure 8 expands the previous findings to a simple, often encountered series terminated net topology. The total transmission line length is still approximately one inch divided equally between the three segments. The driver and receiver models are identical to their original configuration, and a 22-ohm resistor is added to the circuit. To simulate a more typical situation, the net transitions layers from top to bottom, and back to the top, necessitating two vias (13 mil drill, 24 mil pad).

Recall from Figure 2 that the driver impedance is 52.7 ohms as indicated by the wizard. The ideal

series termination would be the transmission line impedance minus the driver impedance (75-52.7 = 22.3 ohms).<sup>1</sup> For simplicity, a 22-ohm resistor is used since this is a standard value. After running the wizard on this topology, it indicates that the effective Z0 is 64.8 ohms and the recommended termination value is 12.1 ohms (64.8–52.7 ohms = 12.1 ohms). From this example, it is easy to see that the capacitance of the topology is affecting the effective impedance and lowering the recommended termination impedance as indicated by the recommended termination resistor (12.1 ohms).

#### **Investigating the Via Contribution**

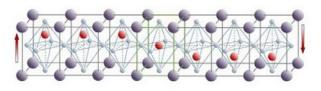

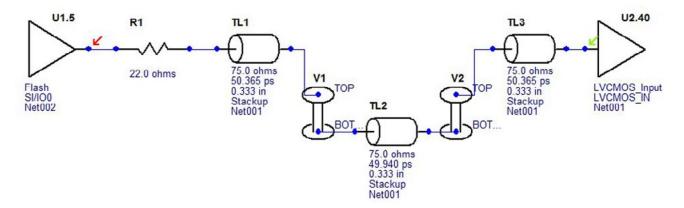

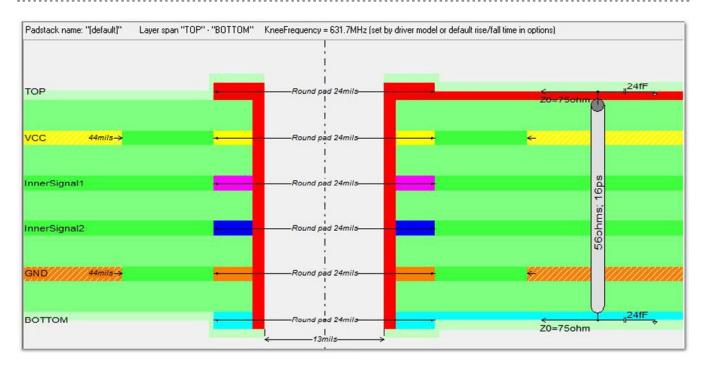

Figure 9 shows the via construction and its transmission line equivalent model (56

Figure 8: The schematic of the series terminated net topology.

Figure 9: The via construction and its transmission line equivalent model.

ohms, 16ps delay). The transmission line model is calculated from the individual LC sections of the via transitioning through the layers and is shown in Figure 10. According to documentation, the pad to plane capacitance of the entry and exit layers are not included in the transmission line equivalent of the via, but are represented by a capacitor to ground.<sup>2</sup>

Referencing Figure 10, the individual inductance and capacitance values are added up to form a lumped model and verified to be approximately 56 ohms and 16ps by the following well known equations.<sup>1</sup>

$$Zo = \sqrt{(L/C)} = \sqrt{(875pH/282fF)} = 55.7 \sim 56\Omega$$

$$Delay = \sqrt{(L \times C) = (875pH \times 282fF)} = 15.7 \sim 16ps$$

After running the wizard with the vias included, the results show the effective Z0 to be 64.8 ohms, and the optimal termination to be 12.1 ohms. What happens if the via characteristics are altered in a way that would better match

# The Absolute Best Value in High Technology Printed Circuit Boards

Since 1979, Eagle Electronics Inc. has provided our Customers with the highest quality Printed Circuit Boards at fair and competitive prices. We are committed to exceeding our Customers' expectations and requirements, acheiving **total customer satisfaction** on each and every job. It's just the way we do business!

001101\_01001

01001010001010101010100001010101010

MANUFACTURERS OF QUALITY PRINTED CIRCUIT BOARDS

With Eagle, you can expect:

- Rapid Response to Quote Requests

- Fair and Competitive Pricing/Costs

- 100% Quality Performance

- 100% On-Time Delivery Performance

- Flexibility Scheduling

- Stock/Consigned Inventory Programs

- Thorough follow-up after job completion

- Total Satisfaction!

click here for a virtual tour of our facility!

www.eagle-elec.com

Figure 10: The transmission line model is calculated from the individual LC sections of the via transitioning through the layers.

the characteristic impedance of the connecting nets (75 ohms)? To see these effects, the via is altered to have a 75 ohm impedance and a 13ps delay (5.4 mil pad, 8 mil drill). Running the wizard again on this scenario shows the effective characteristic impedance is now 67.2 ohms, indicating that the vias are no longer loading the driver as much as before. The drill/pad size chosen for the via aren't entirely realistic. This is merely for purpose of demonstration.

#### **Important Points to Remember**

• The simulator calculates the driver impedance based on the transistor characteristics in the IBIS model and recommends termination based on the topology and characteristic impedance of the system.

• The receiver capacitance parameters including C\_comp, pin capacitance, and package capacitance all impact the loading on the driver, thus changing the effective Z0 parameter.

• The wizard does not appear to consider the system distributive until the interconnection length becomes approximately equal to or longer than 1/6<sup>th</sup> of the driver's transition time.

• When not considered to be a distributive system, changes to the capacitive properties of

the IC are no longer included in the wizard's calculation of the effective Z0 parameter.

• Vias have an effect on the loading of the driver, but their affects can be minimal depending on the driver transition rates. As the driver speeds increase, their effects become more pronounced. **PCBDESIGN**

#### References

1. Signal Integrity: Simplified, ISBN 0-13-066946-6.

2. Mentor Graphics LineSim User Guide, July 2013.

3. Right the First Time, A Practical Handbook on High-Speed PCB and System Design, Volume 2, ISBN 0-9741936-1-5.

4. IBIS (I/O Buffer Information Specification) Version 6.0, September 20, 2013.

Kirk Fabbri is owner of KSPT Engineering Consulting, LLC and electrical engineer for L-3 Communications – Avionics Systems. He can be reached at kirk.fabbri@L-3com.com.

# HIGH-SPEED PCB DESIGN TRAINING

- One-on-one mentoring

- Develop your skills with confidence

- Ensure your next design performs reliably

#### **BEYOND DESIGN**

# Effects of Surface Roughness on High-speed PCBs

by Barry Olney

IN-CIRCUIT DESIGN PTY LTD

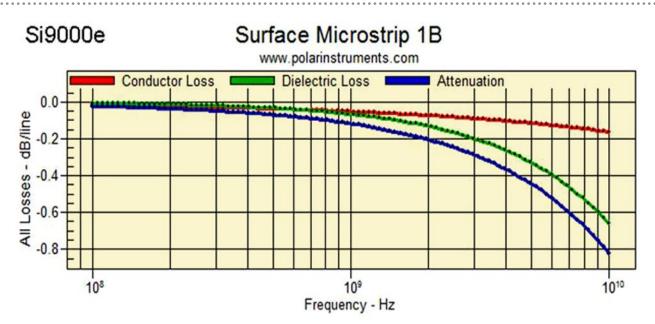

At frequencies below 1GHz, the effect of copper surface roughness on dielectric loss is negligible. However, as frequency increases, the skin effect drives the current into the surface of the copper, dramatically increasing loss. When the copper surface is rough, the effective conductor length extends as current follows along the contours of the surface up and down with the topography of the copper surface. At high frequencies, the effective resistance of the copper increases relative to the additional distance over which the current must transverse the contours of the surface. The total loss comprises of the sum of the conductor loss and dielectric loss.

Whilst it may be possible to manufacture copper foil with a perfect mirror-smooth finish, the foil-to-resin adhesion would be compromised. This would considerably increase the possibility of delamination during the thermal stress of the PCB fabrication and assembly processes. For this reason, a reduced oxide coating is applied to the inner core layers to promote adhesion of the prepreg resin as it flows under the applied heat and pressure to cure.

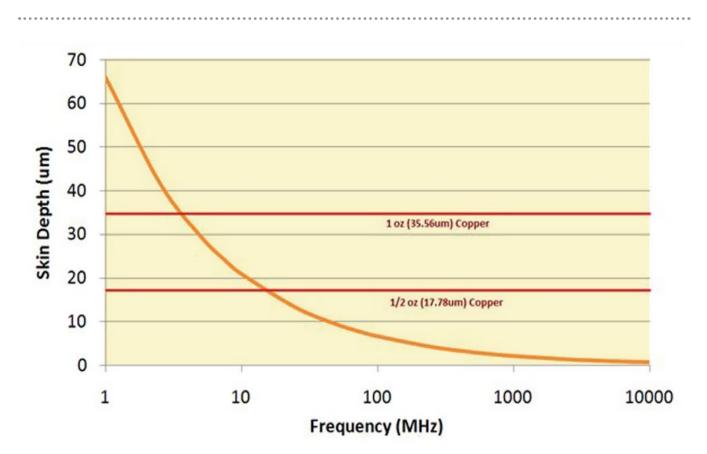

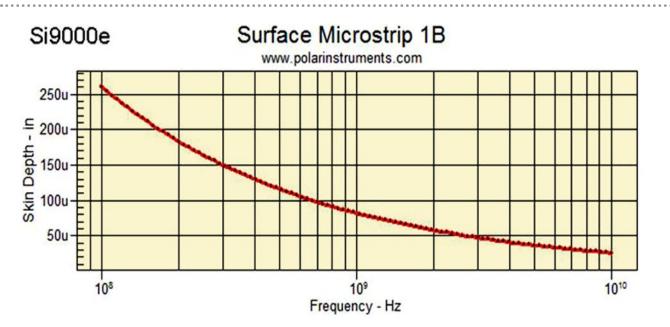

Skin effect is the tendency of an alternating current to become distributed within a conductor such that the current density is largest near the surface, and decreases with greater depths in the conductor. The higher the frequency, the greater the tendency for current to take the path of lower inductance on the outer surface of the conductor. The skin depth is given by:

$$\delta = \sqrt{\frac{2}{2\pi f \,\mu \,\sigma}}$$

where is the skin depth in microns, f is the frequency in MHz, is the magnetic permeabil-

# Quality PCBs from the established industry leader

With over 40 years of experience delivering high quality PCB prototypes, Sunstone Circuits<sup>®</sup> is committed to improving the prototyping process for the design engineer from quote to delivery.

We lead the industry with an on-time delivery rate of over 99%. Plus, our on-site technical support is available every day of the year (24/7/365), giving Sunstone unparalleled customer service.

#### Get a quote instantly at Sunstone.com

- Live customer support 24/7/365

- Over 99% on-time delivery

- Best overall quality & value in industry

- In business for over 40 years

- Online quote & order

- Free 25-point design review

- RF / exotic materials

- Flex / Rigid-Flex boards

- RoHS compliant finishes

- Free shipping & no NREs

- PCB123<sup>®</sup> design software

- Controlled impedance testing

#### **EFFECTS OF SURFACE ROUGHNESS ON HIGH-SPEED PCBS** continues

ity  $(4\pi x 10^{-7} \text{H/m})$  and is the copper conductivity, typically  $(5.6x 10^7 \text{ S/m})$ .

The skin depth (um) can be approximated by:

$$\delta = 66 \sqrt{\frac{1}{f}}$$

Looking at this equation, it is apparent that skin depth decreases with increased frequency. Figure 1 shows the skin depth compared to frequency. At low frequency (1MHz), the skin depth is 66um but this decreases to 0.66um at 10GHz. So, at 10GHz, only the very outer surfaces of the trace carry the current. Also, the red horizontal lines represent the trace copper weight and thickness. This shows that at about 10MHz, a signal traveling in a ½ oz. (17.78um) copper trace would not use the entire trace cross-section, but rather the skin effect would be dominant.

In a previous column, Beyond Design: Surface Finishes for High-Speed PCBs, I pointed out that the nickel content of ENIG surface finish has a ferromagnetic property that can adversely affect electromagnetic fields in the high frequency domain. One could argue that since the nickel is plated on top of the microstrip surface, that it would have little effect on properties of the trace. And that due to the skin effect, the current will travel the path of least inductance, which is on the lower surface of the copper closest to the reference plane. However, it has been found that at approximately 2.7GHz, the resonant behavior of the nickel component in ENIG, increases insertion loss. It is for this reason that solder mask over bare copper (SMOBC) processing should be considered for all highspeed designs.

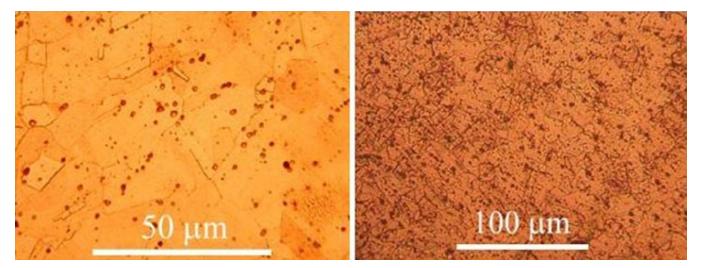

Most substrates are copper clad with either Rolled Annealed (RA) copper, electrodeposited copper (ED) or reverse-treated foil (RTF). RA copper is both smooth and consistent in thick-

Figure 1: Skin depth (um) vs. frequency (MHz).

#### **EFFECTS OF SURFACE ROUGHNESS ON HIGH-SPEED PCBS** continues

Figure 2: Rolled annealed copper (left) and etched copper (right) under an electron microscope (courtesy of University of Cambridge).

ness, but is the most expensive foil. ED copper has the roughest surface and depending on the application and speed requirements, may be perfectly adequate. RTF copper is smoother, and is much the same cost as ED. However, it does exhibit poor peel strength and is prone to delamination. So it is a trade-off between performance and price.

Electrodeposited copper foil is the standard copper used in the laminate industry. ED foil is deposited from a copper solution, at a specific DC voltage, onto a moving polished titanium drum which forms the cathode. The foil is subsequently stripped from the drum. The grain construction formed by this process forms the dendritic "tooth" of the copper on the "bath side" of the copper. The drum side takes on the smooth texture of the polished drum surface onto which it is plated. Figure 3, illustrates a typical inner layer trace cross-section showing the roughness of both the upper and lower copper surfaces.

Rolled copper is made by running a copper strip through successively smaller and smaller gaps in a rolling mill until it reaches the desired thickness. Rolled copper is smoother and can be made very flexible by annealing. Because it is smooth, its bond to laminates is totally dependent on the quality of the treatment it receives and the adhesive properties of the resin system employed. RA copper also has a different grain

Figure 3: Inner layer trace cross-section<sup>[3]</sup>.

structure than ED copper and will etch at a different rate. Much of the RA copper in the laminate industry is used in flexibly circuits, typically bonded to a polyimide film with an acrylic adhesive.

Reverse treated foils involve the subsequent treatment of the smooth side of the electrodeposited copper. Treatment layers are thin, rough coatings that improve adhesion of the base foil to the dielectric material.

To the naked eye, copper clad laminate appears smooth but at the microscopic level, all

#### beyond design

#### **EFFECTS OF SURFACE ROUGHNESS ON HIGH-SPEED PCBS** continues

materials exhibit surface irregularities. If the average incline of the "teeth" of the conducting surface is  $60^{\circ}$ , forming an equilateral triangle, then the increase in surface resistance would be approximately twice that of a dead flat surface. Less severe geometries induce smaller effects. However, a better measure of the surface roughness is the root-mean-square (RMS) height (h<sub>RMS</sub>) of the surface bumps, since the exact profile cannot be established for a working design. Taking the worst case equilateral ridge geometry as a guide, one would expect the RMS roughness to be in the order of 0.29 times the average peak to valley roughness.

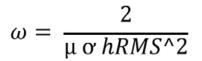

The onset frequency  $(\omega)$  of the RMS surface roughness effect is given by:

where is the magnetic permeability  $(4\pi x 10^{-7} H/m)$  and is the copper conductivity  $(5.98x 10^{-7} S/m)$  and h<sub>RMS</sub> for ED copper.

Therefore, inserting the numbers into the above equation, the onset frequency ( $\omega$ ) of the RMS surface roughness effect is 1.28GHz for ED copper. The smoother the copper surface, the higher the frequency at which surface roughness takes effect.

Also, the effective dielectric constant and hence capacitance is increased due to the increased surface area of the teeth of the rough conductor. This, in turn, lowers the characteristic impedance slightly. The capacitance increases by about 5% for microstrip and 10% for stripline traces that exhibit more roughness. So the effect on impedance is -2% to -5%, respectively.

Although the surface roughness is not generally stated in material manufacturer's datasheets, typical values are 3  $\mu$ m for the outer surface and 6  $\mu$ m for the inner surface. For example, Panasonic's high-performance laminate, Megtron 6 core material, has a dielectric constant (Dk) of 3.4 and loss tangent (Df) of 0.004 at 18GHz. This material is available in standard ED, VLP, SVLP and HVLP (very/super/hyper low profile) foil with average surface roughness of 7–8, 3–4 and 1.5–2 µm respectively.

Isola uses mostly VLP type coppers for their

HSD product offerings. The RTF coppers that Isola offers have roughness values of 4–8 microns. This is standard for FR408HR and IS415 products. VLP2 (Isola's designation) copper is incorporated in high-end products that require the best insertion loss. The roughness for this copper is 2 microns.

So, the smoothest surface HVLP material with 1.5  $\mu$ m average surface roughness, will therefore not exhibit any noticeable surface roughness effect up to 20GHz. Consequently, one would be well advised to take note of the surface roughness properties if your design is running over 1GHz to ensure you choose an appropriate material for the application.

#### **Points to Remember**

- At speeds below 1GHz, the effect of copper surface roughness on dielectric loss in negligible.

- As frequency increases, the skin effect region drives the current into the surface of the copper dramatically increasing loss.

- When the copper surface is rough, the effective conductor length extends as current follows along the contours of the surface up and down with the topography of the copper surface.

- Smooth surfaces considerably increase the possibility of delamination during the thermal stress of the PCB fabrication and assembly processes.

- Skin effect is the tendency of an alternating current to become distributed within a conductor such that the current density is largest near the surface.

- Skin depth decreases with increased frequency.

- The nickel content of ENIG surface finish has a ferromagnetic property that can adversely affect electromagnetic fields in the high frequency domain.

- At approximately 2.7GHz, the resonant behavior of the nickel component in ENIG increases insertion loss. It is for this reason, that SMOBC processing should be considered for all high-speed designs.

- Most substrates are copper clad with either RA, ED, or RTF copper.

- To the naked eye, copper clad laminate ap-

#### **EFFECTS OF SURFACE ROUGHNESS ON HIGH-SPEED PCBS** continues

pears smooth but at the microscopic level, all materials exhibit surface irregularities.

- The onset frequency of the RMS surface roughness effect is 1.28GHz for ED copper.

- Typical values of surface roughness are 3um for the outer surface and 6um for the inner surface.

- The smoothest surface HVLP material with 1.5um average surface roughness, will not exhibit any noticeable surface roughness effect up to 20GHz. **PCBDESIGN**

#### References

1. Barry Olney Beyond Design columns: <u>Surface Finishes for High-Speed PCBs</u> and <u>Material</u> <u>Selection for SERDES Design</u>.

2. "How Surface Roughness Impacts High-Performance PCBs," Judy Warner, Microwave Journal.

3. "Effect of Conductor Surface Roughness upon Measured Loss and Extracted Values of PCB Laminate Material Dissipation Factor," Hinaga, Koledintseva, Anmula and Drewniak. 4. "Signal Transmission Loss due to Copper Surface Roughness in High-Frequency Region," Liew, Okubo, and Hosoi.

5. "Roughness Characterization for Interconnect Analysis," Yuriy Shlepnev, Chudy Nwachukwu.

6. "Signal and Power Integrity Simplified," Eric Bogatin.

7. "High-Speed Signal Propagation," Howard Johnson.

8. The ICD Stackup and PDN Planner, <u>www.</u> <u>icd.com.au</u>

Barry Olney is managing director of In-Circuit Design Pty Ltd (ICD), Australia. This PCB design service bureau specializes in board-level simulation, and has developed the ICD Stackup Plan-

ner and ICD PDN Planner software. To read past columns, or to contact Olney, <u>click here</u>.

#### video Interview

#### **HKPCA Keynote Speech: EMS Trends for 2015**

In his HKPCA keynote speech, IPC President John W. Mitchell discusses some trends IPC sees ahead in 2015 for the global electronics manufacturing services industry. From hot products to changing strategies, Mitchell covers it all.

#### THE PULSE

# **I<sup>3</sup>:** Incident, Instantaneous, Impedance

#### by Martyn Gaudion

POLAR INSTRUMENTS

In my <u>December 2013 column</u>, I discussed "rooting out the root cause" and how sometimes, the real root cause is hidden when digging for the solution to a problem. In that column, I described how sometimes in an attempt to better correlate measured with modelled impedance, fabricators were tempted to "goal seek" the dielectric constant to reduce the gap between predicted and measured impedance.

To cite a common English saying, "There is an elephant in the room," (i.e., something else that is contributing to the error that should be obvious but has perhaps been overlooked). And why is that?

Well, maybe the elephant has been in the room for a while, but it started young and has now grown to a size that cannot be ignored. What is that elephant I am referring to, you ask? DC and AC resistance of the trace is a good possible candidate for an answer here, something that started very small and has grown gradually and perhaps imperceptibly, until now it is often too big to ignore.

Thinking back to first principles, when designers think of the impedance of a transmission line, it has long been commonplace to ignore the losses. So, look at a lossless line where:

$$Z_0 = \sqrt{\frac{L}{C}}$$

And this is true enough in many cases where the copper is thick enough and the PCB trace

# We deliver Advanced PCB Solutions!

# Landless Via Technology

We're the only manufacturer in the world to have perfected a liquid photo-imageable resist (PiP) in electrolytic form, used for all our production.

CLICK TO LEARN MORE

Our unique processes enable us to create and deliver Advanced PCB Solutions that meet the needs of the demanding market at competitive prices!

# Fine line PCB, 2 mil line /space

We have developed a unique set of processes based on electro-depositable liquid photoresist.

CLICK TO LEARN MORE

## Impedance Tolerance <5%!

With our panel plating process combined with continuous foil lamination, our impedance tolerances are second to none!

CLICK TO LEARN MORE

CANDOR INDUSTRIES, INC. ADVANCED PCB SOLUTIONS

www.candorind.com | sales@candorind.com | (416) 736-6306

#### **I<sup>3</sup>: INCIDENT, INSTANTANEOUS, IMPEDANCE** continues

wide enough for the losses to be ignored. Also, from an instantaneous point of view, the L and C scale per unit length and the ratio of L/C is to all intents and purposes independent of length. However, when geometries shrink, characteristics that could be comfortably overlooked in larger dimensions can no longer be ignored and the uncomfortable fact that the equation for transmission lines approximates to:

$$Z_0 = \sqrt{\frac{L+R}{G+C}}$$

R is the resistance per unit length, a combination of the DC and AC resistance, and the G is the conductance per unit length. Unlike the L and C, unfortunately, the R and G cannot be seen as dimensionless and the R piles up along the trace whilst the G stays close to 0 and the two do not divide out. This means that the TDR trace shows the effect of trace resistance presenting an upward slope as ohm upon ohm of combined DC and AC resistance "pile up" on top of the instantaneous impedance.

Without this knowledge, someone trying to analyze why the measured impedance is somewhat higher than the prediction may seek the source of error. The dimensions are hard to argue with if there is access to precision microsections, especially if three or four sections are taken along the trace and all correlate. So, it may be deduced that, given the dimensions are known and provided the impedance measurement system is calibrated and air line verified, that the only unknown is the dielectric constant. However, deducing (derived from the Latin ducere meaning to lead <sup>[1]</sup>) is not foolproof: deduction only works if you are certain of the facts. (For example, when you see a person crying, it's easy to deduce the person is sad. Unless they are happy, of course; sometimes happy people cry.) So deducing that an erroneous Er value is the cause of poor measuring and modeling correlation could be challenged if new facts come to light. Sometimes the clue is in the numbers, and I have seen situations where the Er amount has to be "adjusted" to make the impedance correlate appears to defy the laws of physics: for example, when the Er is adjusted to a lower level than each of the primary individual constituents of the base material. This should be a clue that something else is awry here; this is, as I mentioned earlier, the elephant in the room.

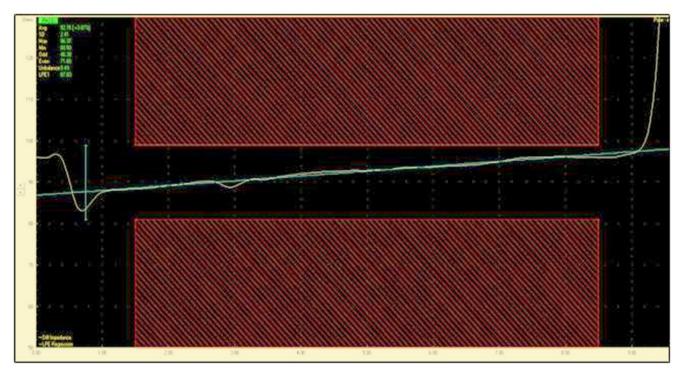

In 2009 at DesignCon, Navarro, Chairet and Mayevskiy<sup>[2]</sup> proposed a technique to measure

Figure 1: Onset of dielectric loss.

#### **I<sup>3</sup>: INCIDENT, INSTANTANEOUS, IMPEDANCE** continues

the instantaneous characteristic impedance of high-frequency cables by removing the resistive elements through a technique called launch point extrapolation (LPE)<sup>[4]</sup>. IPC is now looking at applying this to PCB traces for all the reasons described above. The benefits of applying LPE to PCB trace impedance tests are clear. Linear extrapolation applied to an undisturbed section of the trace and projected back in time to a point close to or at the transition between the probe and the start of the test trace or coupon should remove most of the resistive effects and allow a closer correlation between the modelled impedance and the measured instantaneous impedance. As a precaution and to ensure the copper is not too thin or the line overetched, sometimes a second point is also measured at an imaginary point at the far end of the trace. This ensures that other effects such as trace taper or a higher-than-expected copper resistivity are ruled out.

You might be thinking that "loss" is catered for when measuring insertion loss in the frequency domain, and this is true. But the types of scenario I am referring to in this particular column are those where the lines are operating at "mid" frequencies (i.e., up to one, two or three GHz, where the dielectric losses are still small enough to ignore). The resistive losses in copper appear at these frequencies because of a couple of reasons: one is the use of thinner copper and the other is that line widths are shrinking too. This means that there are starting to be small but significant losses from DC upwards. To add to that, the onset of skin effect in copper starts to take effect at lower frequencies than need to be considered in the case of dielectric losses.

So it is in this "middle ground" of thin copper/narrow traces and low GHz operating speeds that fabricators and designers start to see impedance traces which rise over time, i.e., distance, with the cumulative build up of resistive effects. This effectively means you need to look at the operating frequency band and the trace geometry and the combination of these to choose the most appropriate method for measurement.

With low-frequency wide traces, trace capacitance is the predominant issue.

With medium-frequency 1 or 2 GHz wide traces, lossless impedance:

$$Z_0 = \sqrt{\frac{L}{C}}$$

Figure 2: Skin depth.

#### **I<sup>3</sup>: INCIDENT, INSTANTANEOUS, IMPEDANCE** continues

Figure 3: TDR trace with LPE and sloping impedance result.

Medium frequency 1 or 2 GHz narrow traces, impedance:

$$Z_0 = \sqrt{\frac{L+R}{C}}$$

At high frequencies, 3 GHz and above, insertion loss is significant:

$$Z_0 = \sqrt{\frac{L+R}{G+C}}$$

In conclusion, when looking at transmission line measurements and specifying transmission line characteristics, you should ensure that if you are working with narrow traces and thin copper and your frequencies are not yet high enough to worry about dielectric losses, you should take a look at your TDR waveforms for a significant slope in the measurement area. Consider specifying the measurement of instantaneous impedance by using Launch Point Extrapolation. **PCBDESIGN**

#### References

1. "Deduce" definition: <u>www.vocabulary.com</u>.

2. Luis Navarro, Timothy Chairet, Eugene Mayevskiy, "Application of Launch Point Extrapolation Technique to Measure Characteristic Impedance of High-Frequency Cables with TDR," DesignCon 2009.

3. Lossy Traces: Where and How to use Loss Compensation, <u>Polar Instruments Application</u> <u>Note AP156</u>.

4. Measuring Impedance on Thin Traces with Launch Point Extrapolation, <u>Polar Instru-</u><u>ments Application Note AP8505</u>.

Martyn Gaudion is CEO of Polar Instruments. To contact him, click here. Monterey, California February 23–26, 2015

FlexTechAlliance

Presented by

# Same Great Conference in a New Location!

1111

- » Best Technical Program by and for the industry

- » State-of-the-art conference and exhibition facility

- » Two adjacent 4-star hotels to choose from

- » Easy access to Silicon Valley and other San Francisco Bay Area locations

- » Regional airport served by most major airlines

- » Regular shuttles to San Francisco & San Jose Airports

- » Ideal location for both networking and relaxing with clients & colleagues

- » Iconic California experiences easily available: wine tasting, whale watching, Cannery Row tours, legendary golf courses, breathtaking BigSur coastline

More information at www.2015FLEX.com.

#### **QUIET POWER**

# Effects of DC Bias on Ceramic Capacitors

by Istvan Novak ORACLE

The density of multilayer ceramic capacitors (MLCC) has increased tremendously over the years. While 15 years ago a state-of-the-art X5R 10V 0402 (EIA) size capacitor might have had a maximum capacitance of 0.1 uF, today the same size capacitor may be available with 10 uF capacitance. This huge increase in density unfortunately comes with a very ugly downside: the capacitance is now very sensitive to DC and AC bias across the part.

MLCCs are manufactured with different types of ceramics. With a given case size, dielectric thickness and plate count, the capacitance is proportional to the dielectric constant of the ceramic: the higher the dielectric constant, the more capacitance we get from the same structure. For low-loss, high-performance RF and microwave applications Class 1 materials are used <sup>[1]</sup>. These provide very good and stable electrical characteristics, practically zero bias and temperature dependence, but their relative dielectric constant is below 100 and hence capacitance density is low. In a 0402-size package we may get 1000 pF with 50V rating. If we need more capacitance in a small package, we have to select Class 2 (or Class 3) ceramics <sup>[2]</sup>, which are ferroelectric materials with a dielectric constant in the 200 to 14000 range.

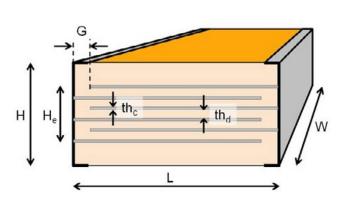

A typical two-terminal MLCC internal geometry is shown in Figure 1. The two vertical metal terminals connect every other horizontal plate, creating a number of parallel-connected parallel-plate capacitor segments. The stack of capacitor plates fills the H total capacitor body height with an effective height of  $H_e$ . The nonconnected capacitor plates should not come out to the sidewall of the capacitor body, they are pulled back to create a small G gap. If, for now, we ignore these gaps and consider  $H=H_e$ and G=0, each pair of adjacent capacitor plates creates a  $C_u$  unit capacitance:

$$C_u = \varepsilon_0 \varepsilon_r \frac{LW}{th_d}$$

where  $e_0$  is the dielectric constant of vacuum, or 8.85 pF/m, and  $e_r$  is the relative dielectric constant of the ceramic material. In the capacitor body altogether we have N plate pairs, where N (if we ignore the end effects) can be approximated with

$$N = \frac{H}{th_d + th_c}$$

The total capacitance from the N pairs of capacitor plates gives us the following formula:

$$C = \varepsilon_0 \varepsilon_r \frac{LWH}{th_d (th_d + th_c)}$$

In the above expression the LWH product is the volume of the capacitor body. For regular ceramic capacitors the H height typically does not exceed the W width; for a given case size

Figure 1: Approximate internal geometry of MLCC.

#### INTRODUCING **COOLSPAN® TECA** thermally & electrically conductive adhesive

#### Rogers can help by being your reliable conductive adhesive film source

Get the heat out of those high-power PCBs. COOLSPAN® Thermally & Electrically Conductive Adhesive (TECA) Films are ideal for dissipating heat in high-frequency circuits. COOLSPAN adhesives feature outstanding thermal conductivity (6 W/m/K) and reliable thermal stability. Keep things cool, with Rogers and COOLSPAN TECA film.

#### CONTACT YOUR SUPPORT TEAM TODAY

#### **MEET YOUR COOLSPAN® TECA FILM SUPPORT TEAM**

Leading the way in... • Support • Service • Knowledge • Reputation

#### SCAN THE CODE TO GET OUR CONTACT INFO.

**Dale Doyle** Application Manager Western

35 O

Development Manager Southern Territory (U.S.) & South

Kent Yeung Regional Sales Director

Visit us in San Diego, Booth 1701

If you are unable to scan a VR code please visit our www.rogerscorp.com Support Team website at www.rogerscorp.com/coolspan

#### **EFFECTS OF DC BIAS ON CERAMIC CAPACITORS** continues

this creates the LW<sup>2</sup> upper limit for the volume. To increase capacitance, either the  $e_r$  relative dielectric constant has to increase, or the  $th_d$  and/or  $th_c$  thickness values have to decrease. In case the conductor thickness is much less than the dielectric thickness, the capacitance grows with the inverse square of the dielectric thickness. This gives a convenient scaling possibility to improve the volumetric density of ceramic capacitors: if we use thinner dielectric layers, in the given case size we can produce more and more capacitance.

However, as we make each dielectric layer thinner, the E field strength from the same V voltage applied across the part grows proportionally:

$$E = \frac{V}{th_d}$$

Also, if we increase the e<sub>r</sub> dielectric constant, the D electric displacement field will grow proportionally:

$$D = \varepsilon_0 \varepsilon_r E$$

If we plot the relationship between E and D in high dielectric constant ferroelectric materials (Figure 2), D will not follow it proportionally and eventually the curve flattens out, which is called saturation.

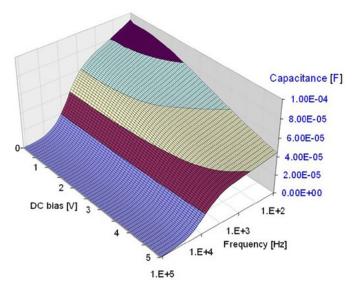

Over the many years as we, the users, kept asking for more capacitance in the same package, this scaling helped the industry to give us what we asked for. But we get not only more capacitance; we also get more bias sensitivity. Today the detailed data sheets from major MLCC vendors give us the typical bias sensitivity we can expect from MLCC parts, but unfortunately this kind of data is not a guaranteed specification. In case we want to collect our own data, the techniques and instrumentation is available in professional form <sup>[4]</sup>. When we look at the data sheet values or at our own measured data <sup>[5]</sup>, we can see in some applications we can easily lose up to 80% of the capacitance just to DC bias effects.

We can also use simple homemade equipment to measure complex reflections and com-

Figure 2: Relationship between the E and D fields in ferroelectric materials.

plex impedance and from that we can back-calculate capacitance. Figure 3 shows the DC bias effect measured with a homemade vector-network analyzer on a 100 uF MLCC.

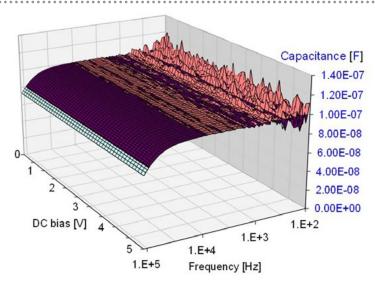

The 3D surface is put together from multiple individual frequency sweeps, each with a different DC bias value across the capacitor. The DC bias voltage is shown on the left axis; the right axis shows frequency. Note that the capacitance depends not only on the bias voltage, but also on frequency. None of these dependencies are present in Class 1 ceramic capacitors. Figure 4 shows the bias-dependence surface for a 0.1 uF COG MLCC.

The 3D surface of Figure 4 is flat in both directions until we start approaching the series resonance frequency of the part. There is an increasing noise on the measured surface at very low frequencies. At 100 Hz the impedance magnitude of a 0.1 uF capacitor is more than 10 kOhm. The noise illustrates the limitation of the simple home-made instrumentation when we try to measure kilo-ohm impedance values in two-port shunt-through connection.

So, be careful when you use a 6.3-rated Class 2 ceramic capacitor in a 5V application: a big percentage of the capacitance may be gone. The good news is that this bias dependence is hardly present in tantalum and aluminum capacitors, film capacitors and printed-circuit laminates. **PCBDESIGN**

### **EFFECTS OF DC BIAS ON CERAMIC CAPACITORS** continues

Figure 3: Capacitance as a function of frequency and DC bias, as measured on a 100 uF 4V Class 2 MLCC part.

Figure 4: Capacitance as a function of frequency and DC bias, as measured on a 0.1 uF Class 1 MLCC part.

### References

- 1. Wikipedia: Class 1 ceramic capacitors.

- 2. Wikipedia: Class 2 ceramic capacitors.

- 3. Wikipedia: Permittivity.

4. Accuracy Improvements of PDN Impedance Measurements in the Low to Middle Frequency Range," DesignCon 2010, February 1–4, 2010, Santa Clara, CA.

5. DC and AC Bias Dependence of Capacitors Including Temperature Dependence," DesignCon East 2011, September 27, 2011, Boston, MA.

Dr. Istvan Novak is a distinguished engineer at Oracle, working on signal and power integrity designs of mid-range servers and new technology developments. With 25 patents to his name, Novak is co-author

of "Frequency-Domain Characterization of Power Distribution Networks." To read past columns, or to contact Novak, <u>click here</u>.

#### **BOB AND ME**

#### . . . . . . . . . . . . . . . . . .

## Controlled Impedance: A Real-World Look at the PCB Side

#### by Dan Beaulieu and Bob Tarzwell

**DAN:** When I was a very young man, way back in the taped artwork days of the 1970s, I was a program coordinator (a fancy name for expeditor) at Rockwell's Maine Electronics in Lisbon, Maine. One of my programs was the Burroughs Scientific Processor (BSP) created by Burroughs Corporation, based in Paoli, Pennsylvania. We were building very high-tech 14- and 16-layer boards for this program. We were told that these BSP computers were so powerful that the first one was already "running" the airport in Narita, Japan.

Now, this was 1975, mind you. The only computer I had ever seen was being installed in a glass room at the company. I was walking around tracking my PCBs with a pen and clipboard and I had no idea what "running an airport with a computer" even meant. By the way, I did get a chance to see a BSP system being built. It was quite an impressive sight, especially since they had slimmed it down to three refrigerator/freezer-sized units. I remember being amazed that something that small could run an entire airport!